SiCやGaNを超える省エネ性能を理論的に持つ次世代パワー半導体材料「ルチル型二酸化ゲルマニウム(r-GeO₂)」の実用化に向けて、立命館大学発スタートアップのPatentixが2026年3月31日、デプレッション型MOSFETのトランジスタ動作実証に成功したと発表した。ヘテロエピタキシャル膜を用いたr-GeO₂のMOSFET動作実証は世界初の報告だという。

r-GeO₂はバンドギャップが4.68eVと、SiCの3.3eVを大きく上回る超ワイドバンドギャップ半導体材料だ(eVはエレクトロンボルト、半導体の電気的特性を表す単位)。バンドギャップが大きいほど高電圧・高温環境での動作や低損失な電力変換が可能になる。現在主流のSiCはシリコン比で約40%の省エネ効果があるとされているが、r-GeO₂ではさらにその90%程度の省エネ効果が理論的に示されており、電力変換損失の大幅な低減を期待できる次世代材料として注目されている。

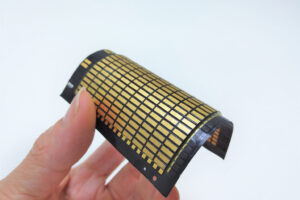

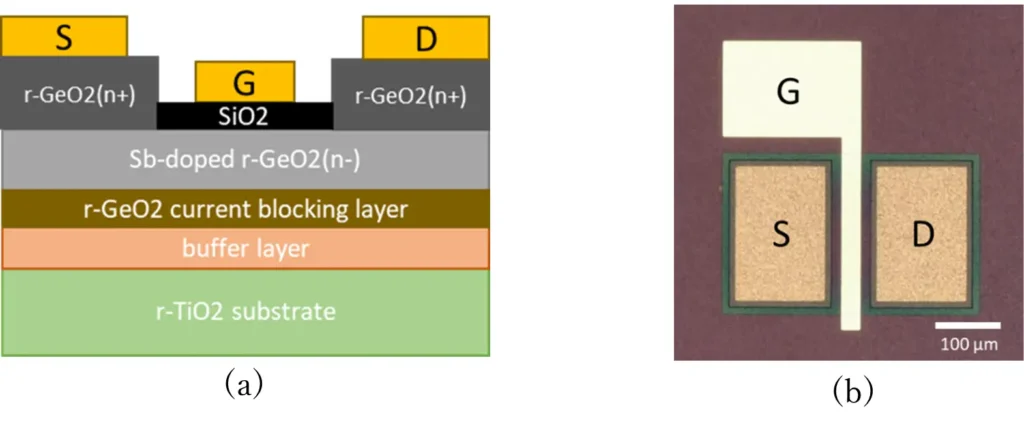

今回の成果は、Patentixがこれまでに積み上げてきた独自の成膜技術によるものだ。ルチル型二酸化チタン(r-TiO₂)基板上に不純物をドーピングしたr-GeO₂膜で電流遮断層を形成し、その上に選択成長でSbドープのn-チャネル層(厚さ160nm)とソース・ドレインのn+層を成膜したMOSFET構造を作製した。ゲート絶縁膜にはSiO₂(75nm)、電極にはPt/Tiを使用している。デプレッション型MOSFETとは、ゲート電圧が0のときにオン状態となるトランジスタ動作方式で、今回はr-GeO₂のn型層のみで作製できる構造として選択された。

作製したデバイスの電気特性を評価したところ、ゲート電圧によりドレイン電流が5桁以上のオン・オフ比で変化し、デプレッション型のトランジスタ動作を確認した。またゲート電圧印加に伴う特性変動(ヒステリシス)が小さく抑制されており、プロセス条件の最適化が進んでいない段階でも欠陥の少ないゲート絶縁膜界面が形成されていると考えられるという。

Patentixは2022年12月の設立以来、世界初のN型導電性確認(2024年9月)、ショットキーバリアダイオードの動作実証(2024年11月)と着実に成果を積み上げてきた。今回のMOSFET動作実証は、同材料でエンハンスメント型MOSFETを実現するための土台となる重要なマイルストーンだ。同社は2027年にエピウエハーの市場投入を計画しており、「琵琶湖半導体構想」のもと、東レやアイシンなど大手企業も連携した産業化に向けた動きが加速している。

関連情報

プレスリリース:https://prtimes.jp/main/html/rd/p/000000025.000128234.html